TUJUAN

- Memahami klasifikasi dari ICs digital

- Mengetahui klasifikasi dari ICs digital

- Melatih keterampilan menggunakan aplikasi proteus.

KOMPONEN

Flame Detector (Flame Sensor)

AND gates

Gerbang AND akan berlogika 1 apabila semua inputnya berlogika 1, namun bila salah satu atau semua keluarannya berlogika 0 maka keluarannya berlogika 0.

Perhatikan Tabel kebenaran dibawah untuk menjelaskan gerbang AND

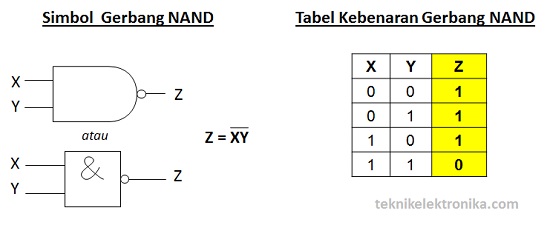

NAND gates

Arti NAND adalah NOT AND atau BUKAN AND, Gerbang NAND merupakan kombinasi dari Gerbang AND dan Gerbang NOT yang menghasilkan kebalikan dari Keluaran (Output) Gerbang AND. Gerbang NAND akan menghasilkan Keluaran Logika 0 apabila semua Masukan (Input) pada Logika 1 dan jika terdapat sebuah Input yang bernilai Logika 0 maka akan menghasilkan Keluaran (Output) Logika 1.

Tabel kebenaran gerbang NAND

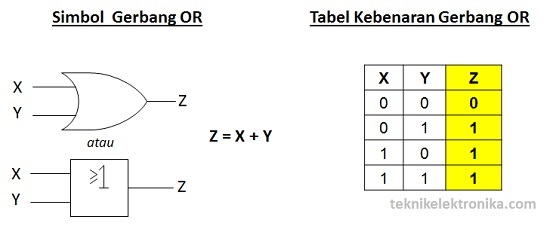

OR gates

Gerbang OR memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang OR akan menghasilkan Keluaran (Output) 1 jika salah satu dari Masukan (Input) bernilai Logika 1 dan jika ingin menghasilkan Keluaran (Output) Logika 0, maka semua Masukan (Input) harus bernilai Logika 0.

Simbol yang menandakan Operasi Logika OR adalah tanda Plus (“+”). Contohnya : Z = X + Y.

Perhatikan tabelk kebenaran gerbang OR

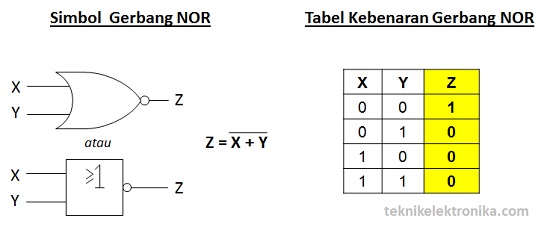

Gerbang NOR (OR INVERT)

NOR gates

Arti NOR adalah NOT OR atau BUKAN OR, Gerbang NOR merupakan kombinasi dari Gerbang OR dan Gerbang NOT yang menghasilkan kebalikan dari Keluaran (Output) Gerbang OR. Gerbang NOR akan menghasilkan Keluaran Logika 0 jika salah satu dari Masukan (Input) bernilai Logika 1 dan jika ingin mendapatkan Keluaran Logika 1, maka semua Masukan (Input) harus bernilai Logika 0.

Perhatikan tabel kebenaran gerbang NOR

DASAR TEORI

Kebanyakan flip flop memiliki input sinkron dan asinkron. Input sinkron adalah yang efek pada output flip-flop disinkronkan dengan input jam. Input R, S, J, K dan D semuanya masukan sinkron. Input asinkron adalah input yang beroperasi secara independen dari sinkron masukan dan sinyal jam masukan. Ini sebenarnya menimpa masukan karena statusnya menggantikan status dari semua input sinkron dan juga input jam. Mereka memaksa keluaran flip-flop untuk pergi ke yang telah ditentukan status terlepas dari status logika input sinkron. Input PRESET dan CLEAR adalah contoh masukan asinkron. Saat aktif, input PRESET dan CLEAR menempatkan flip-flop Q keluaran masing-masing dalam status '1' dan '0'. Biasanya, ini adalah input LOW yang aktif. Saat diinginkan bahwa fungsi flip-flop sesuai dengan status input sinkronisnya, input asinkron disimpan dalam keadaan tidak aktif mereka. Juga, kedua input asinkron, jika tersedia pada flip-flop tertentu, tidak dibuat aktif secara bersamaan.

- CLOCK AKTIF TINGGI (PERPINDAHAN DARI O KE 1) DAN KEDUA INPUT ASYNCHRONOUS AKTIF RENDAH

- KAKI BERNILAI 1

- KAKI J BERNILAI 1

LINK DOWNLOAD

- Download HTML : KLIK DI SINI !!!

- Download Rangkaian : KLIK DI SINI !!!

- Download Video Rangkaian : KLIK DI SINI !!!

Tidak ada komentar:

Posting Komentar